# Birzeit University Faculty of Engineering and Information Technology Department of Computer Systems Engineering First Semester - 2016/2017

Course: Computer Architecture – ENCS 437

**Project: Design of Single Cycle MIPS Using Logisim**

#### 1. Project Objectives

After completing this project, you will:

- · Learn how to design a single-cycle CPU

- · Verify the correct operation of your single-cycle CPU design

## 2. Subset of the MIPS Instructions included in CPU Design

In this section, we will illustrate the design of a single-cycle CPU for a subset of the MIPS instructions, shown in Table 1. These include the following instructions:

- ALU instructions (R-type): add, sub, and, or, xor, slt

- Immediate instructions (I-type): addi, slti, andi, ori, xori

- Load and Store (I-type): lw, sw

- Branch (I-type): beq, bne

- Jump (J-type): j

Although this subset does not include all the integer instructions, it is sufficient to illustrate the design of datapath and control. Concepts used to implement the MIPS subset are used to construct a broad spectrum of computers. For each instruction to be implemented, you need to identify all the steps that need to be performed for the execution of each instruction expressed in register transfer level (RTL) notation. These steps are summarized below for all the instructions to be implemented:

\_ R-type Fetch instruction: Instruction ← MEM[PC]

Fetch operands: data1 ← Reg(Rs), data2 ← Reg(Rt)

Execute operation: ALU\_result ← func(data1, data2)

Write ALU result: Reg(Rd) ← ALU\_result

Next PC address:  $PC \leftarrow PC + 4$

\_ I-type Fetch instruction: Instruction ← MEM[PC]

Fetch operands: data1  $\leftarrow$  Reg(Rs), data2  $\leftarrow$  Extend(imm16)

Execute operation: ALU\_result  $\leftarrow$  op(data1, data2)

Write ALU result: Reg(Rt) ← ALU\_result

Next PC address:  $PC \leftarrow PC + 4$

\_ BEQ Fetch instruction: Instruction ← MEM[PC] Fetch operands: data1 ← Reg(Rs), data2 ← Reg(Rt)

Equality: zero  $\leftarrow$  subtract(data1, data2)

Branch: if (zero) PC  $\leftarrow$  PC + 4 + 4 $\times$ sign\_ext(imm16)

else PC  $\leftarrow$  PC + 4

LW Fetch instruction: Instruction ← MEM[PC]

Fetch base register: base  $\leftarrow$  Reg(Rs)

Calculate address: address ← base + sign\_extend(imm16)

Read memory: data  $\leftarrow$  MEM[address] Write register Rt: Reg(Rt)  $\leftarrow$  data Next PC address: PC  $\leftarrow$  PC + 4

**Table 1**: MIPS instructions subset implemented in CPU design.

| Instruction |                           | Meaning          | Format  |                 |                 |                                   |   |      |

|-------------|---------------------------|------------------|---------|-----------------|-----------------|-----------------------------------|---|------|

| add         | rd, rs, rt                | addition         | op6 = 0 | rs <sup>5</sup> | rt⁵             | rd⁵                               | 0 | 0x20 |

| sub         | rd, rs, rt                | subtraction      | op6 = 0 | rs <sup>5</sup> | rt⁵             | rd <sup>5</sup> 0 0x2             |   | 0x22 |

| and         | rd, rs, rt                | bitwise and      | op6 = 0 | rs <sup>5</sup> | rt <sup>5</sup> | rd <sup>5</sup> 0 0x2             |   | 0x24 |

| or          | rd, rs, rt                | bitwise or       | op6 = 0 | rs <sup>5</sup> | rt⁵             | rd <sup>5</sup> 0 0x <sup>2</sup> |   | 0x25 |

| xor         | rd, rs, rt                | exclusive or     | op6 = 0 | rs <sup>5</sup> | rt <sup>5</sup> | rd <sup>5</sup> 0 0x              |   | 0x26 |

| slt         | rd, rs, rt                | set on less than | op6 = 0 | rs <sup>5</sup> | rt <sup>5</sup> | rd <sup>5</sup> 0 0               |   | 0x2a |

| addi        | rt, rs, im <sup>16</sup>  | add immediate    | 0x08    | rs <sup>5</sup> | rt⁵             | im <sup>16</sup>                  |   |      |

| slti        | rt, rs, im <sup>16</sup>  | slt immediate    | 0x0a    | rs <sup>5</sup> | rt <sup>5</sup> | im <sup>16</sup>                  |   |      |

| andi        | rt, rs, im <sup>16</sup>  | and immediate    | 0x0c    | rs <sup>5</sup> | rt <sup>5</sup> | im <sup>16</sup>                  |   |      |

| ori         | rt, rs, im <sup>16</sup>  | or immediate     | 0x0d    | rs <sup>5</sup> | rt <sup>5</sup> | im <sup>16</sup>                  |   |      |

| xori        | rt, im <sup>16</sup>      | xor immediate    | 0x0e    | rs <sup>5</sup> | rt <sup>5</sup> | im <sup>16</sup>                  |   |      |

| lw          | rt, im <sup>16</sup> (rs) | load word        | 0x23    | rs <sup>5</sup> | rt <sup>5</sup> | im <sup>16</sup>                  |   |      |

| SW          | rt, im <sup>16</sup> (rs) | store word       | 0x2b    | rs <sup>5</sup> | rt <sup>5</sup> | im <sup>16</sup>                  |   |      |

| beq         | rs, rt, im <sup>16</sup>  | branch if equal  | 0x04    | rs <sup>5</sup> | rt <sup>5</sup> | im <sup>16</sup>                  |   |      |

| bne         | rs, rt, im <sup>16</sup>  | branch not equal | 0x05    | rs <sup>5</sup> | rt <sup>5</sup> | im <sup>16</sup>                  |   |      |

| j           | im <sup>26</sup>          | jump             | 0x02    |                 |                 | im <sup>2</sup>                   | 6 |      |

\_ SW Fetch instruction: Instruction  $\leftarrow$  MEM[PC] Fetch registers: base  $\leftarrow$  Reg(Rs), data  $\leftarrow$  Reg(Rt)

Calculate address: address ← base + sign\_extend(imm16)

Write memory: MEM[address] ← data

Next PC address: PC  $\leftarrow$  PC + 4

\_Jump Fetch instruction: Instruction ← MEM[PC]

Target PC address: target ← PC[31:28], Imm26, '00'

Jump: PC ← target

## 3. Datrapath Design

The first step in designing a datapath is to determine the requirements of the instruction set in terms of components. These include the following:

- \_ Memory

- \_ Instruction memory where instructions are stored

- \_ Data memory where data is stored

- \_ Registers

- \_ 32 × 32-bit general purpose registers, R0 is always zero

- \_ Read source register Rs

- \_ Read source register Rt

- \_ Write destination register Rt or Rd

- \_ Program counter PC register and Adder to increment PC

- \_ Sign and Zero extender for immediate constant

- \_ ALU for executing instructions

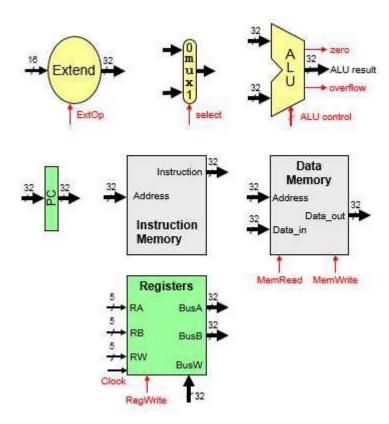

The needed components are summarized below:

- \_ Combinational Elements

- \_ ALU, Adder

- \_ Immediate extender

- \_ Multiplexers

- \_ Storage Elements

- \_ Instruction memory

- \_ Data memory

- \_ PC register

- \_ Register file

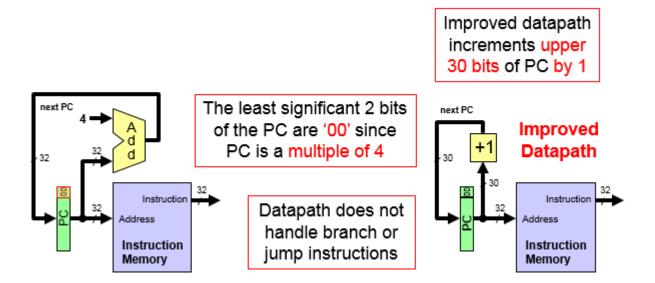

We can now assemble the datapath from its components. For instruction fetching, we need:

- \_ Program Counter (PC) register

- \_ Instruction Memory

- \_ Adder for incrementing PC

The implementation of the instruction fetch process is illustrated in Figure 12.1. Since all the MIPS instructions are 32-bit instructions (i.e. each instruction is stored in 4 address locations) and since the instruction memory will be aligned on 4-byte boundary, the least significant 2-bits of instruction addresses will always be 0. Thus, it is sufficient the update the most significant 30 bits of the PC.

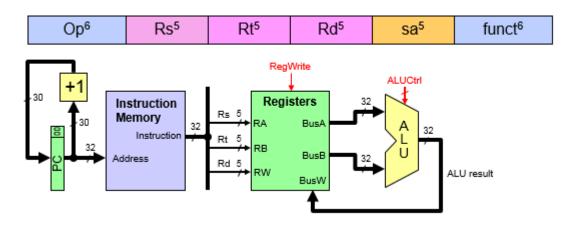

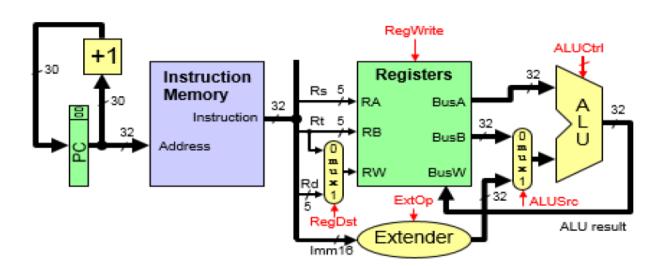

To execute R-type instructions, we need to read the content of registers Rs and Rt, perform an ALU operation on their contents and then store the result in the register file to register Rd. The datapath for executing R-type instructions is shown in Figure below.

The control signals needed for the execution of R-type instructions are:

- ALUCtrl is derived from the funct field because Op = 0 for R-type

- \_ RegWrite is used to enable the writing of the ALU result

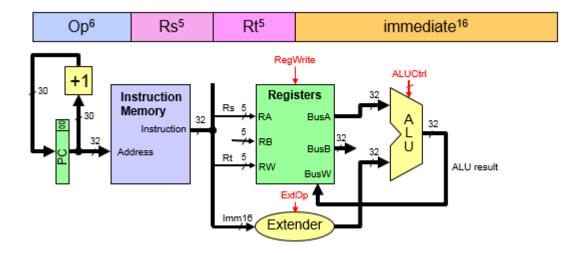

The execution of the I-type instructions is similar to the R-type instructions with the difference that the second operand is an immediate value instead of a register and that the destination register is determined by Rt instead of Rd. The 16-bit immediate value needs to be extended to a 32-bit value by either adding 16 0's or by extending the sign bit. The datapath for the execution of I-type instructions is given in Figure below.

The control signals needed for the execution of I-type instructions are:

- \_ ALUCtrl is derived from the Op field

- RegWrite is used to enable the writing of the ALU result

- \_ ExtOp is used to control the extension of the 16-bit immediate

Next we combine the datapath for executing both the R-type and I-type instructions as shown in Figure below. A multiplexer is added to select between Rd and Rt to be connected to Rw in the register file to determine the destination register. Another multiplexer is added to select the second ALU input as either the source register Rt data on BusB or the extended immediate.

The control signals needed for the execution of either R-type or I-type instructions are:

- \_ ALUCtrl is derived from either the Op or the funct field

- \_ RegWrite enables the writing of the ALU result

- ExtOp controls the extension of the 16-bit immediate

- RegDst selects the register destination as either Rt or Rd

- \_ ALUSrc selects the 2nd ALU source as BusB or extended immediate

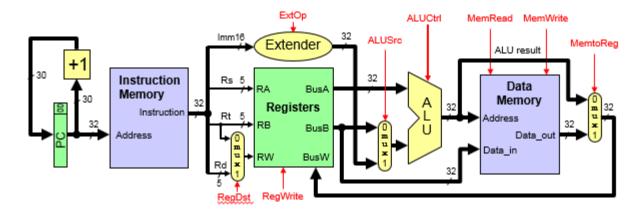

To execute the load and store instructions, we need to add data memory to the datapath. For the load and store instructions, the ALU will be used to compute the memory address by adding the content of register Rs coming through BusA and the sign-extended immediate value. For the load instruction, we need to write the

output of the data memory to register file. Thus, a third multiplexer is added to select between the output of the ALU and the data memory to be written to the register file. BusB is connected to Datain of Data Memory for store instructions. The updated CPU with the capability for executing load and store instructions is shown here.

The additional control signals needed for the execution of load and store instructions are:

- MemRead for load instructions

- \_ MemWrite for store instructions

- \_ MemtoReg selects data on BusW as ALU result or Memory Data\_out

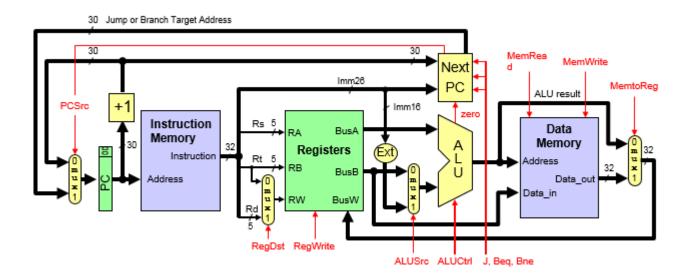

For executing jump and branch instructions, we need to add a block, called NextPC, to compute the target address. In addition, we need to add a multiplexer to select the input to the PC register to be either the incremented PC address or the target address generated by NextPC block. For branch instructions, the ALU is used to perform subtract operation to subtract the content of the two compared registers Rs and Rt. The updated data path to include the execution of the jump and branch instructions is given below.

The additional control signals needed for the execution of jump and branch instructions are:

- \_ J, Beq, Bne for jump and branch instructions

- Zero condition of the ALU is examined

- \_ PCSrc = 1 for Jump & taken Branch

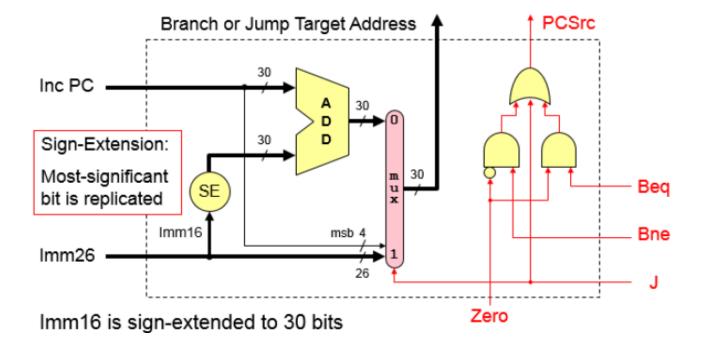

The details of the NextPC block are illustrated in Fug. 12.7. For the jump instruction, the target address is computed by concatenating the upper 4 bits of PC with Imm26 (i.e. the 26-bit immediate value). However, for

branch instructions the target address is computed by adding the sign-extended version of the 16-bit immediate value with the incremented value of PC. Note that the immediate value is computed by the assembler as [Terget - (PC + 4)]/4. Thus, to restore the target address we need to multiply the immediate value by 4 (i.e. shift it 2 bits to the left) and then add PC+4 to it.

Since we are updating the most significant 30-bits of PC, this is achieved by adding PC+1 to the immediate value. The PCSrc signal is set when a branch instruction is taken or a jump instruction is executed, which is implemented by the equation PCSrc = J + (Beq. Zero) + (Bne. Zero').

## 4. Control Unit Design

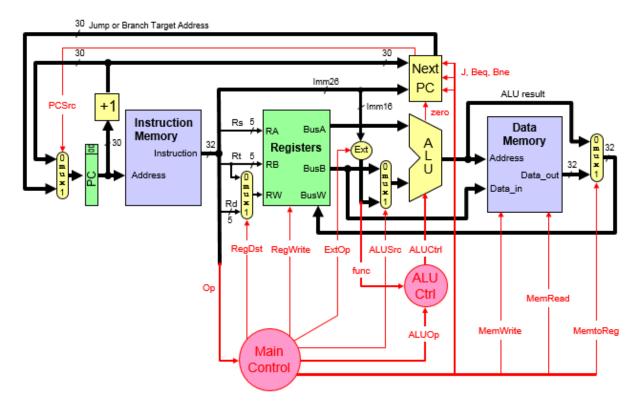

The control unit of the single-cycle CPU can be decomposed into two parts Main Control and ALU Control. The Main Control unit receives a 6-input opcode and generates all the needed control signals other than the ALU control. However, the ALU Control gets a 6-bit function field from the instruction and ALUCtrl signal from the Main Control. The single cycle CPU including the datapath and control unit is illustrated in the following Figure.

To design the Main Control unit, we need to generate the control table which lists for each instruction, the control values needed to execute the instruction. This is illustrated in Table 2. **Table 12.2**: Main Control Signal Values.

| Ор     | Reg<br>Dst | Reg<br>Write | Ext<br>Op | ALU<br>Src | ALU<br>Op | Beq | Bne | J | Mem<br>Read | Mem<br>Write | Mem<br>toReg |

|--------|------------|--------------|-----------|------------|-----------|-----|-----|---|-------------|--------------|--------------|

| R-type | 1 = Rd     | 1            | х         | 0=BusB     | R-type    | 0   | 0   | 0 | 0           | 0            | 0            |

| addi   | 0 = Rt     | 1            | 1=sign    | 1=lmm      | ADD       | 0   | 0   | 0 | 0           | 0            | 0            |

| slti   | 0 = Rt     | 1            | 1=sign    | 1=lmm      | SLT       | 0   | 0   | 0 | 0           | 0            | 0            |

| andi   | 0 = Rt     | 1            | 0=zero    | 1=lmm      | AND       | 0   | 0   | 0 | 0           | 0            | 0            |

| ori    | 0 = Rt     | 1            | 0=zero    | 1=lmm      | OR        | 0   | 0   | 0 | 0           | 0            | 0            |

| xori   | 0 = Rt     | 1            | 0=zero    | 1=lmm      | XOR       | 0   | 0   | 0 | 0           | 0            | 0            |

| lw     | 0 = Rt     | 1            | 1=sign    | 1=lmm      | ADD       | 0   | 0   | 0 | 1           | 0            | 1            |

| SW     | Х          | 0            | 1=sign    | 1=lmm      | ADD       | 0   | 0   | 0 | 0           | 1            | х            |

| beq    | Х          | 0            | Х         | 0=BusB     | SUB       | 1   | 0   | 0 | 0           | 0            | х            |

| bne    | Х          | 0            | Х         | 0=BusB     | SUB       | 0   | 1   | 0 | 0           | 0            | х            |

| j      | Х          | 0            | Х         | х          | х         | 0   | 0   | 1 | 0           | 0            | Х            |

Once we have the Control Table, the control unit can be design easily using a 6x64 decoder that has the 6-bit opcode as input and a signal for each instruction as output. Then each control signal will be either an OR gate of the instructions signals that make this signal 1 or a NOR gate of the instructions signals that make this signal 0, which ever results in a smaller gate size. The decoder and the logic equations for the Main Control signals are shown here.

Similarly, the ALU control signals equations can be derived based on the 6-bit function field and the ALUOp signal generated by the Main Control unit.

It should be observed that the control unit signals equation can also be derived using K-map technique without using a decoder. However, using a decoder makes the design of the control unit simple. You may refer to Appendix D of the text book for more details on the design of the control unit.

#### 5. Tasks

- 1. For the instructions in the CPU that you are going to design, list all the steps that are needed for the execution of each instruction in RTL notation.

- 2. Ensure that you have all the needed components for constructing your datapath.

- 3. Design the datapath for your CPU and model it using logisim.

- 4. Apply the needed values for the control signals needed for the execution of each instruction to ensure correct functionality of the datapath.

- 5. Design the control unit of your CPU and model it using logisim.

- 6. Test the correct functionality of the control unit by ensuring that it generates the correct control signal values for each instruction.

- 7. Model the single cycle CPU design in logisim by combining the datapath and control units.

- **8.** Test the correct functionality of your CPU by storing all the implemented instructions in the instruction memory and verifying the correct execution of each instruction.

# 6. Grading Policy:

The grade will be divided according to the following components:

- Correctness of the datapath design

- Correctness of the control unit design (room for innovation and bonus)

- Demo program produces correct results

- Completeness of integration of datapath and control

- Test cases and coverage of different instructions all cases

- Documentation

- Team Work (groups of two or three): Participation and contribution to the project

## DeadLine: December 15, 2016

#### To Submit:

- Complete report with proper snapshots covering all tasks

- Logisim files (designs and test cases)